請注意:A71x39與A71D39 Sleep mode下FIFO Reg的狀態有所差異

本篇說明用戶使用A7139 X/D版本時,若有使用到sleep mode,需特別注意X/D,2者在流程設計上有所差異

1. A71D39 目前設計進 sleep mode 是"不能" read / write FIFO 的,且D版進入Sleep mode時,FIFO寄存器是會掉電的,而X版可以lock住狀態。

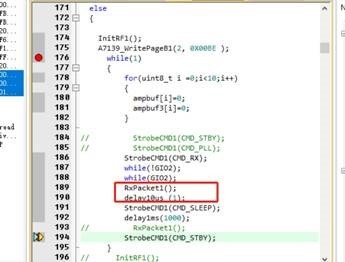

2. x版流程它可以是RX ==>sleep==>read data==>standby==>Rx,也就是說x版可以先Rx將data緩存在fifo reg裡,然後進sleep,喚醒後再去read rx buf data,然後重新進入standby輪循RX。

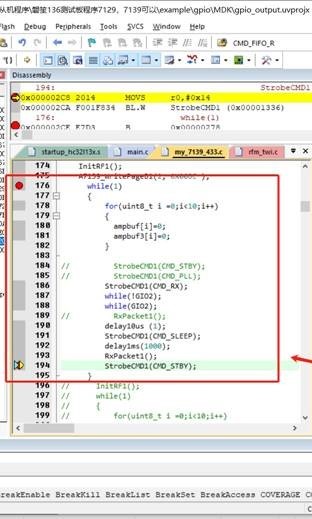

3. 但D版的不行,它必須改成 Rx==>read data==>sleep==>standby==>Rx,也就是D版必須在進入Sleep前,就將fifo reg裡的rx buf data釋放掉,否則一旦進入sleep mode,FIFO Reg掉電,資料就會被丟棄,當再次standby喚醒去read fifo reg時,rx buf就會出現FIFO的数据全部是0x00