如何解決A71D30出現因Ckgen Calibration 異常,使得T/RX Data Rate 誤差過大,無法通訊問題

本篇為Debug A71D30 因 Ckgen Calibration 異常,使得T/RX出現Data Rate 誤差過大,無法正常通訊問題

Define and Verify Escape and Root Cause:

因電源 Startup 電路設計不同,部份 A71D30 IC 會在 POR(Power on Reset) 時容易發生 RF Cal. FAIL 或異常現象。

底下提供解法:

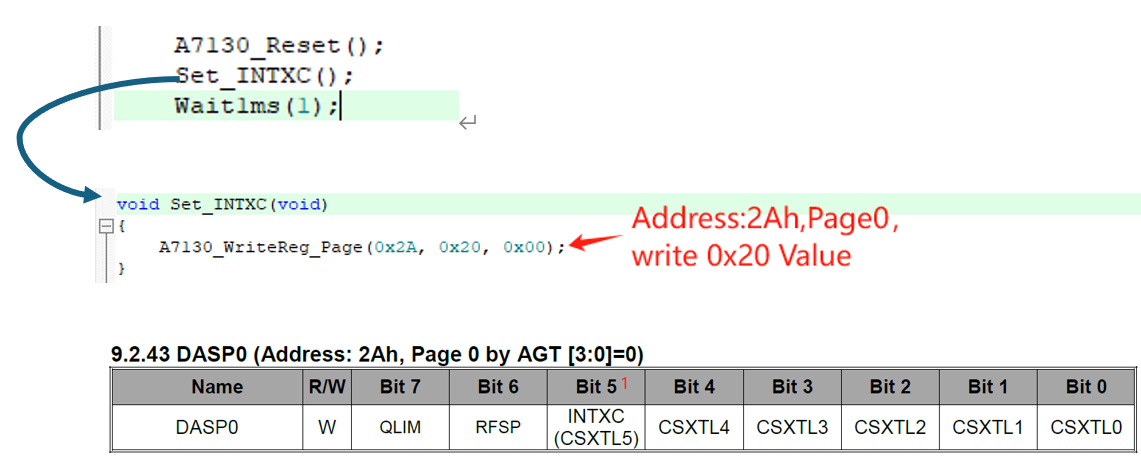

1. RF ResetèINTXC(Address:2Ah,Page 0, bit 5)=’1’èdelay 1ms

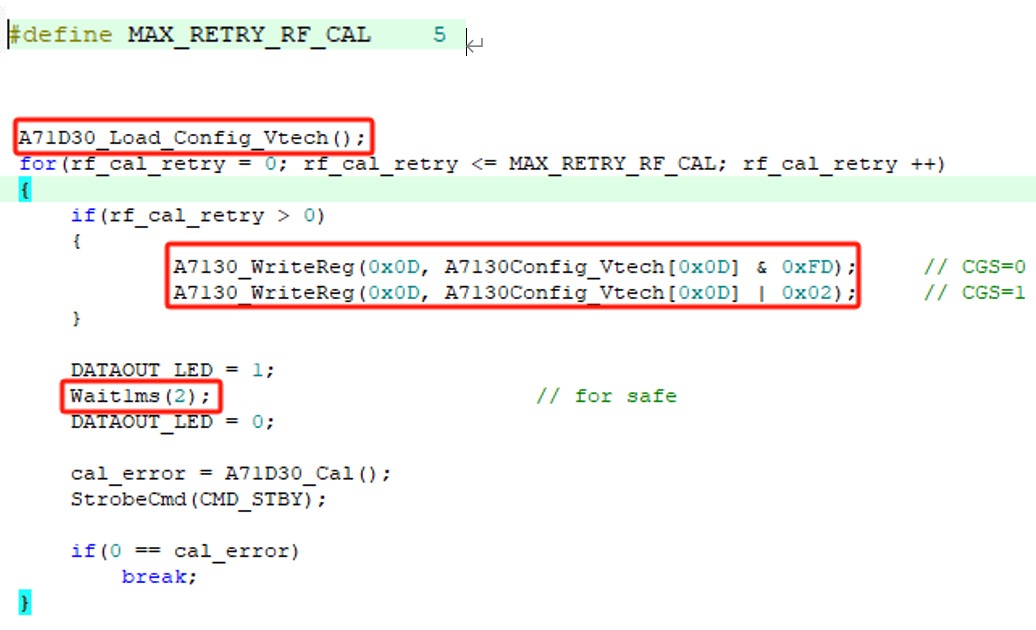

2. Load CONFIG èdelay 2msè RF Cal. 若 FAIL 則 CGS寫0再寫1 èdelay 2msèRepeat RF Cal.( 最多重新Cal. 5次)