FIFO Extension介紹 & 使用Amiccom M0核 MCU控制 A7128做T/RX 256Byte

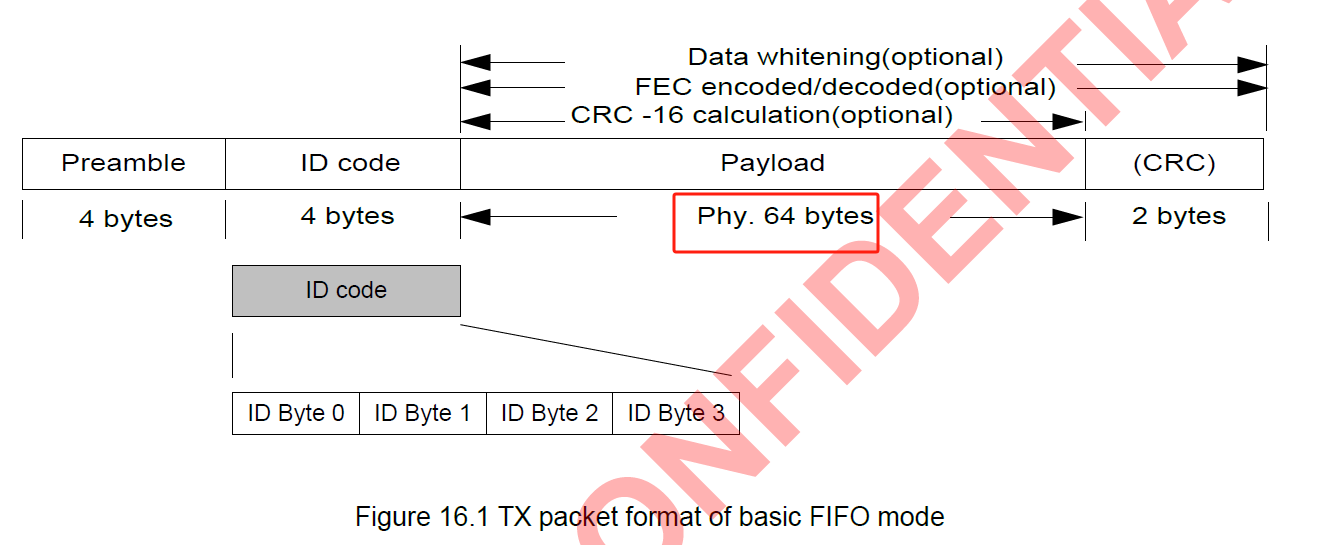

1. Basic FIFO介紹: 一般FIFO 的PHY(物理空間) Payload最大長度為64Byte,也就是說當用戶需要傳輸超過64Byte資料時,要不就是分成多包的Basic FIFO 封包傳輸,但因為每包的開頭都會有前導碼+ID的存在,如此一來會浪費許多時間在重複傳輸(前導碼+ID)

因此Amiccom RF IC 支持使用FIFO Extension功能,讓用戶可以在一包中只發射一次"前導碼+ID"後面就能跟隨著>64Byte的資料數據。

2. FIFO Ext介紹: 由於上述介紹過的Amiccom RF IC FIFO 的PHY(物理空間) Payload最大長度為64Byte,然而FIFO Ext也是需要依照這個規則進行,只是我們會將超出64Byte的資料拆分成數個小封包來進行

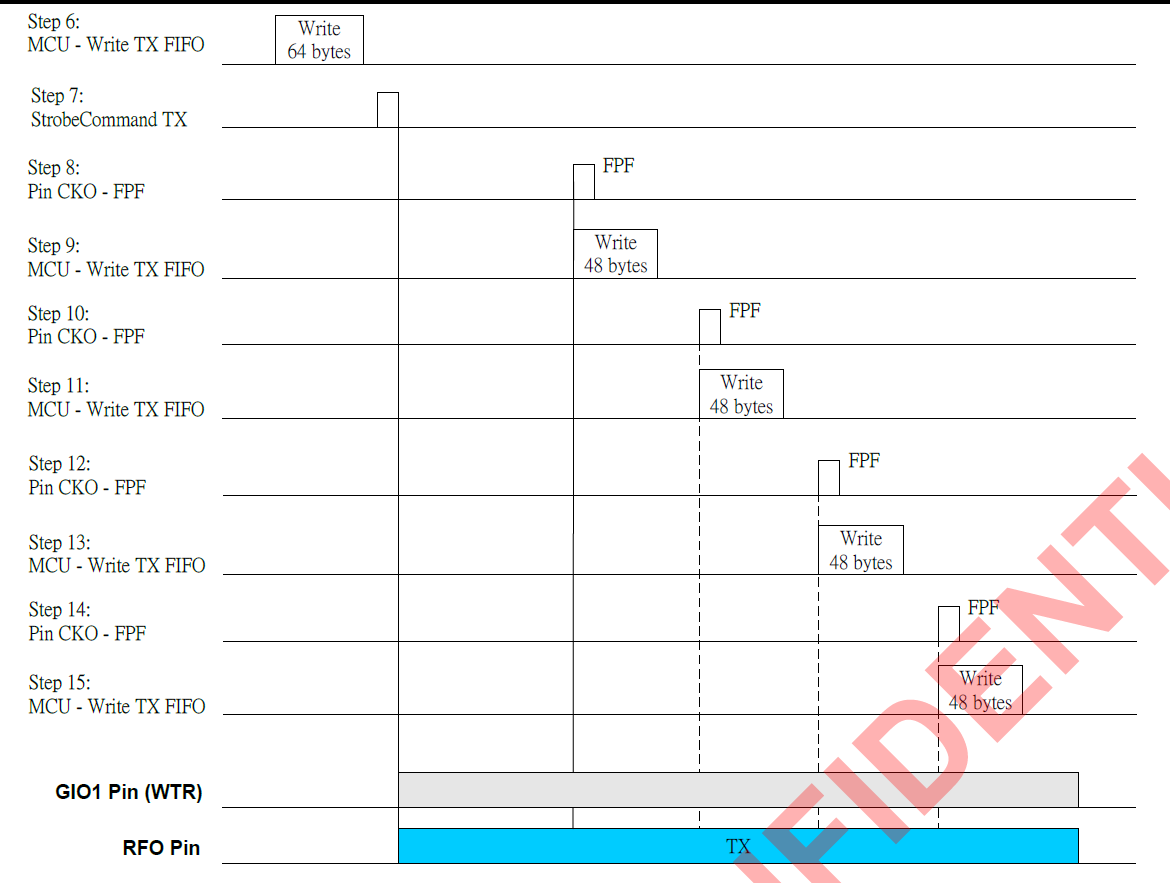

TX部分:

==============================================================================================================

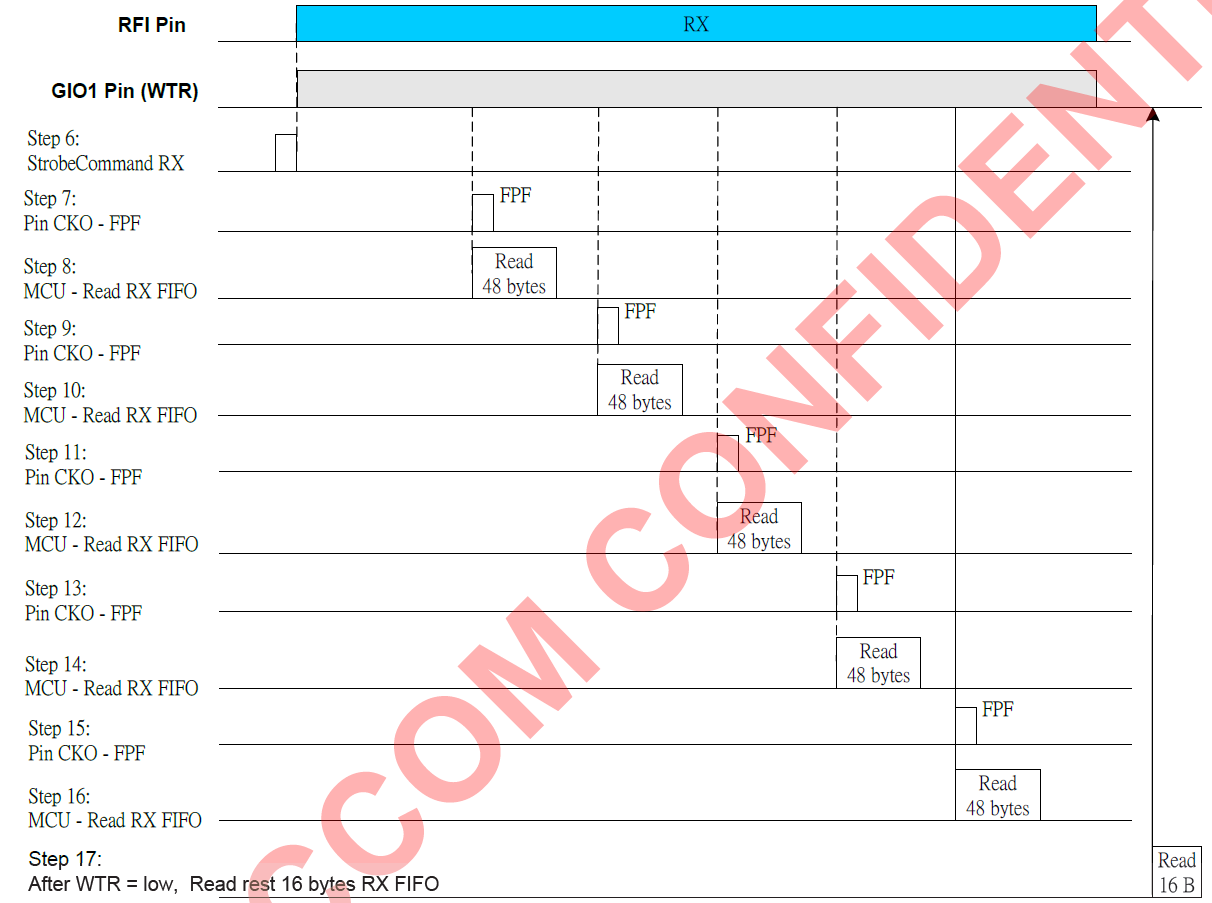

RX部分:

底下為開發FIFO Ext時須注意的事項

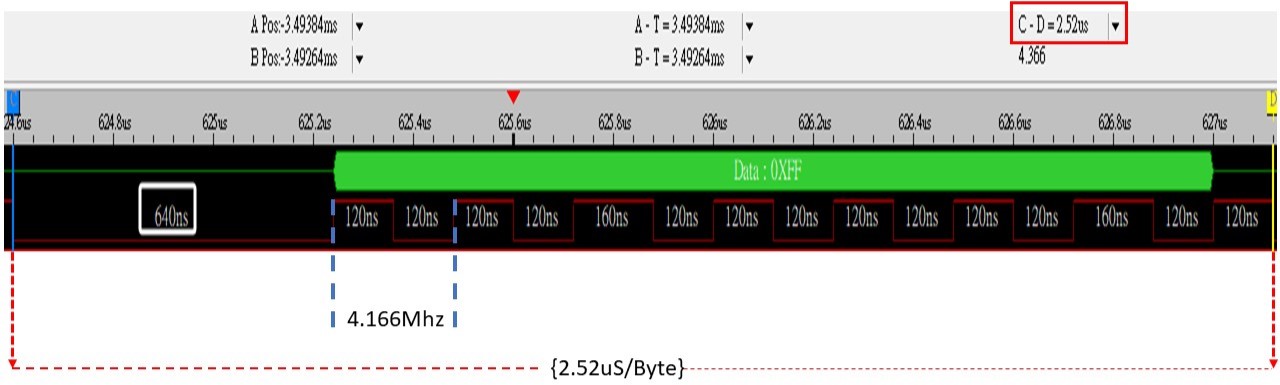

SPI速度需要是(RF DataRate的速度+500K),舉例A7128來說,DataRate若使用max=2Mbps的話,那麼SPI的速度就需要 ">"2.5Mhz以上,這中間包刮軟件 執行將每個 byte的SPI Data填入到硬件SPI Buffer的時間

以Amiccom 的A3117M0為例,640nS為軟件將SPI Data填入HW SPI Buffer的時間,實際上A3117M0的HW SPI可以達4.166Mhz

計算每個bit 的SPI 速度:2.52uS/8(bit)=0.315us/bit==3.17Mhz(有符合>2.5Mhz),所以可以繼續使用

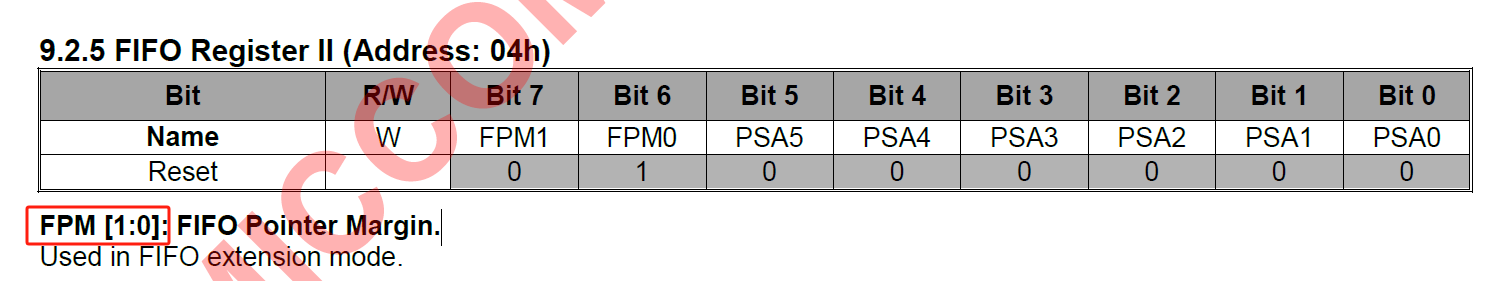

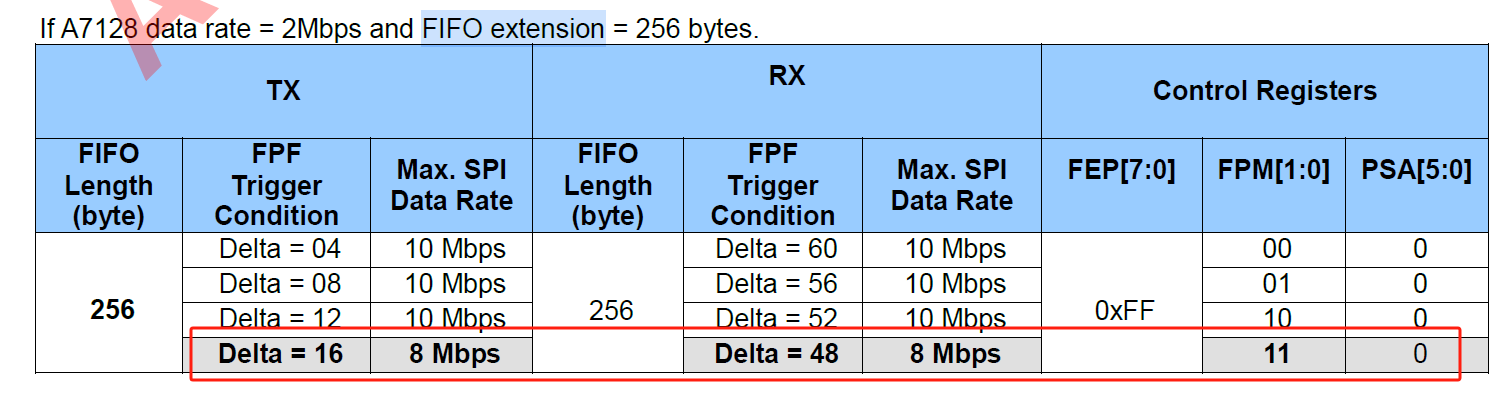

Amiccom 每顆RF IC 的FIFO Max length有所不同,需要去看手冊上的"FEP"寄存器大小,以A7128為例,FIFO length is equal to (FEP [7:0] +1),也就是說A7128的FIFO長度最大為255+1=256個Byte

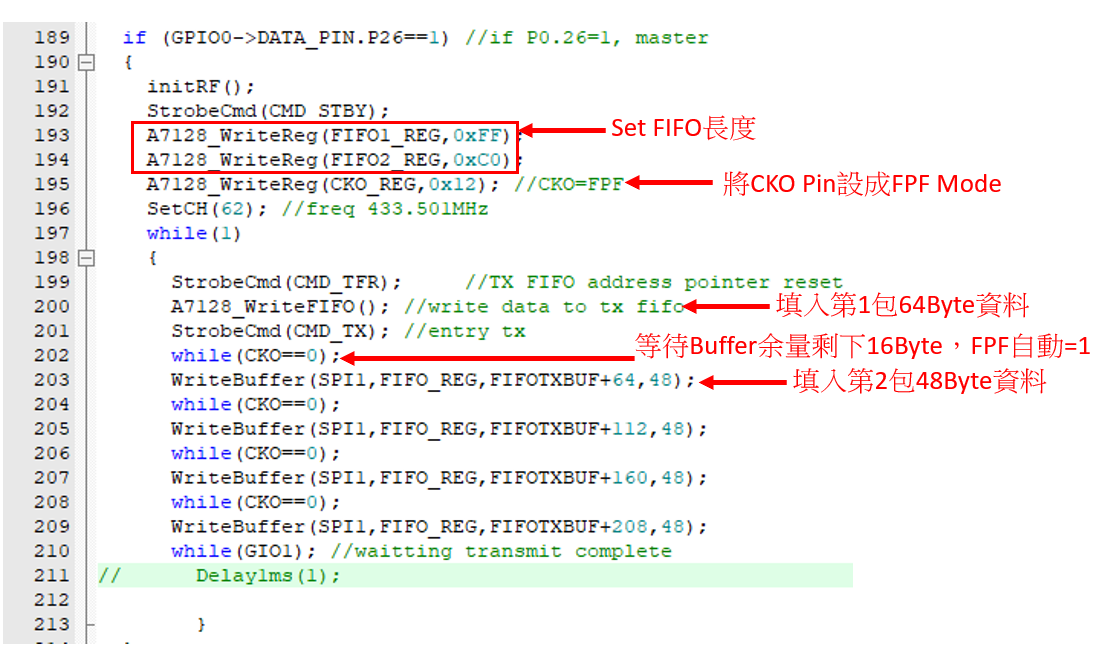

3. 如第2章FIFO Ext介紹的,FIFO Ext將超出64Byte的資料拆分成數個小封包來進行,所以就會出現"余量"(margin)的問題,可以調整"FPM"決定margin的大小(預設[11]為16 Byte),這也就是為什麼FIFO Ext需要拆分成1st(64Byte)==>2nd(48 Byte)==>3rd (48 Byte)==>.......的原因,他需要在包與包之前預留16Byte的余量,好讓RF IC可以透過CKO Pin定義成FPF Mode(FIFO Pointer Flag),去中斷MCU,告知MCU,RF IC的FIFO Buffer已經剩下16 Byte了,需要盡快填入下一個48 Byte的資料進去FIFO Buffer

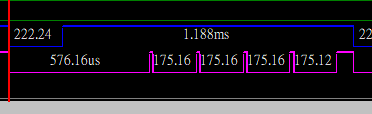

以 A3117M0控制A7128為例,實測FIFO Ext Max 256 Byte需花時:222.24us+1.188ms~=1.41ms

4. 代碼部分:

A7128-A40_MCU A3117M0-FIFO Extension.zip

A7128-A40_MCU A3117M0-FIFO Extension.zip

LA File:

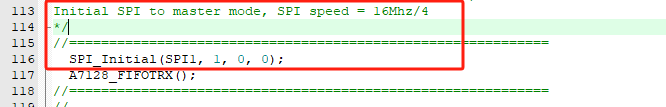

1.先設定好A3117M0 SPI HW Speed=Xtal/4==>Xtal選用16M,所以SPI Speed=4Mhz

2.執行FIFO TX/RX

TX部分:

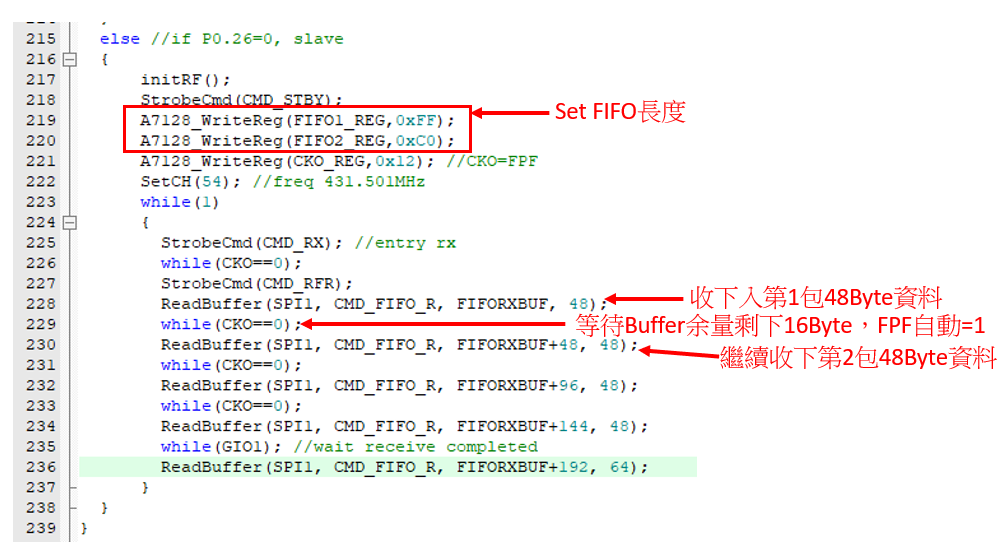

RX部分:反之先收下48 Byte,剩餘16Byte的余量,等待FPF=1時,繼續收下第2包 48 Byte 資料